# **SN100 Series - Secure Element** with Crypto Library

Security Target Lite Rev. 3.5 — 21 April 2021

**Evaluation document COMPANY PUBLIC**

#### **Document information**

| Information                                                                                                                                                    | Content                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords NXP, SN100 Series, SN100x Single Chip Secure Element and NFC Controller, Crypto Library, Common Criteria, Security Target Lite, SB2.1 C25 / C48 / C58 |                                                                                                                                                                                                                                                                                                                                                                                  |

| Abstract                                                                                                                                                       | This document is the Security Target Lite of the Secure Element of the SN100x Single Chip Secure Element and NFC Controller Series with IC Dedicated Software, developed and provided by NXP Semiconductors. The Secure Element complies with Evaluation Assurance Level 6 of the Common Criteria for Information Technology Security Evaluation Version 3.1 with augmentations. |

# SN100 Series - Secure Element with Crypto Library

**Security Target Lite**

## **Revision history**

| Revision Date Desc number |     | Date       | Description                            |

|---------------------------|-----|------------|----------------------------------------|

|                           | 3.5 | 21.04.2021 | Derived from full Security Target v3.5 |

## 1 ST Introduction

#### 1.1 ST Reference

"SN100 Series - Secure Element with Crypto Library", Security Target Lite, Revision 3.5, NXP Semiconductors, 21 April 2021.

### 1.2 TOE Reference

The TOE is named "SN100 Series - Secure Element with Crypto Library". It consists of

- the Secure Element subsystem of the IC hardware platform SN100x <sup>1</sup>,

- IC Dedicated Software (Crypto Library, Services Software and IC Dedicated Support Software), and

- documentation describing the usage of the TOE.

The TOE is available in three configuration named

- B2.1 C25

- B2.1 C48

- B2.1 C58

In this document the TOE is abbreviated to "SN100\_SE" 2.

### 1.3 TOE Overview

## 1.3.1 Usage and major security functionality

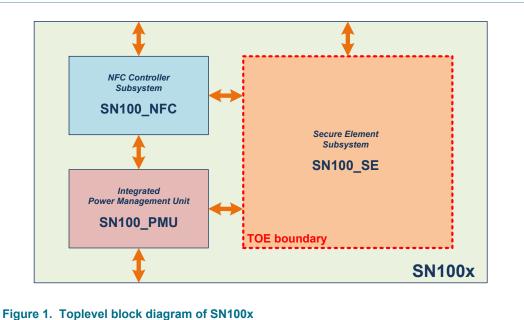

The SN100x Single Chip Secure Element and NFC Controller Series combines on a single die an Embedded Secure Element and a NFC Controller. The two subsystems are called "SN100\_SE" and "SN100\_NFC". The NFC Controller ist not part of the TOE.

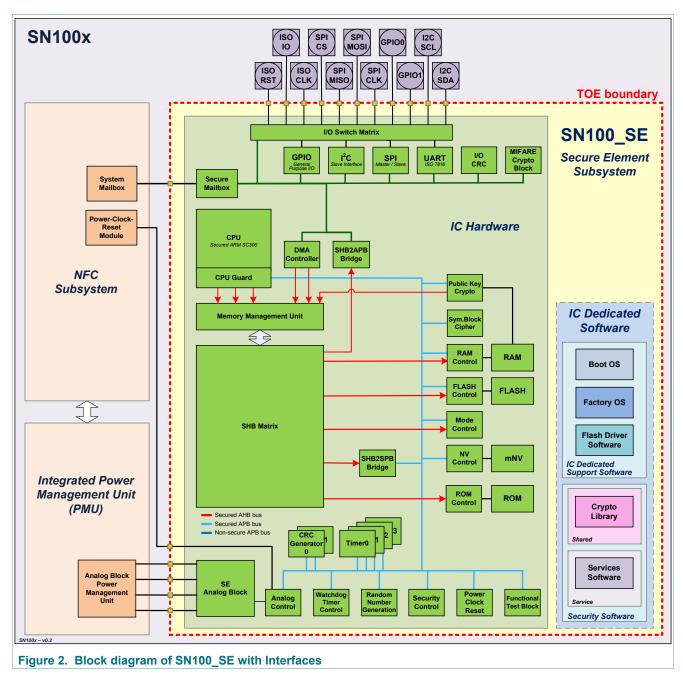

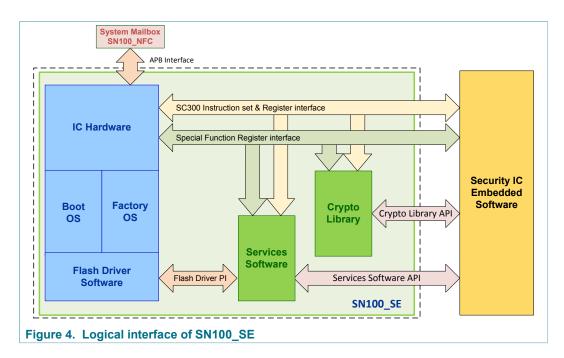

The Embedded Secure Element SN100\_SE is based on a Flash-based secure microcontroller platform. A high frequency clocked ARM SC300 core along with state of the art cryptographic hardware coprocessors brings secured applications to a new level in performances and security (see <a href="Section 1.3.1.1">Section 1.3.1.1</a>). The TOE includes Security Software, composed of Services Software and a Crypto Library, that can be used by the Security IC Embedded Software (see <a href="Section 1.3.1.2">Section 1.3.1.2</a>).

The TOE is integral part of the SN100x IC. Note that SN100x without any Security IC Embedded Software for the TOE is available for NXP internal use only.

#### 1.3.1.1 IC Hardware

The hardware part of the SN100\_SE incorporates an high frequency clocked ARM SC300 processor, a Public-Key Cryptography (PKC) coprocessor and a Direct Memory Access (DMA) controller, which are all connected over a Memory Management Unit (MMU) to a bus system. This bus system gives access to memories, hardware peripherals and communication interfaces.

SN100 Series - Secure Element with Crypto Library

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

<sup>1</sup> The "x" in SN100x indicates the type of the SN100 series (representing e.g. the NFC Controller configuration)

<sup>2</sup> Both notations SN100\_SE and SN100x\_SE are used throughout TOE documentation. Both terms shall be considered as synonym.

The ARM SC300 processor is a security enhanced variant of the ARM Cortex M3. It includes the SC300 core and the Nested Vector Interrupt Controller (NVIC). The core implements the ARMv7-M architecture, which supports a subset of the Thumb instruction set. The PKC coprocessor provides large integer arithmetic operations, which can be used by Security IC Embedded Software for asymmetric-key cryptography. Hardware peripherals include coprocessors for symmetric-key cryptography and for calculation of error-detecting codes, and also a random number generator. The DMA controller manages data transfers over communication interfaces like ISO/IEC 7816 compliant interface, Serial Peripheral Interface (SPI), I2C interface and the Secure Mailbox Interface. On-chip memories are Flash memory, ROM and RAMs. The Flash memory can be used to store data and code of Security IC Embedded Software. It is designed for reliable non-volatile storage.

SN100\_SE is offered with the NXP Trust Provisioning Service, which involves secure reception, generation, treatment and insertion of customer data and code at NXP.

The documentation of SN100\_SE includes a product data sheet, several product data sheet addenda, a user guidance and operation manual, and service documentation. This documentation describes secure configuration and secure use of SN100\_SE as well as the services provided with it.

The security functionality of SN100\_SE is designed to act as an integral part of a security system composed of SN100\_SE and Security IC Embedded Software to strengthen it as a whole. Several security mechanisms of SN100\_SE are completely implemented in and controlled by SN100\_SE. Other security mechanisms must be treated by Security IC Embedded Software. All security functionality is targeted for use in a potential insecure environment, in which SN100\_SE maintains

- correct operation of the security functionality,

- integrity and confidentiality of data and code stored to its memories and processed in the device,

- controlled access to memories and hardware components supporting separation of different applications.

This is ensured by the construction of SN100\_SE and its security functionality.

SN100 SE basically provides

- hardware to perform computations on multiprecision integers, which are suitable for public-key cryptography,

- hardware to calculate the Data Encryption Standard with up to three keys,

- hardware to calculate the Advanced Encryption Standard (AES) with different key lengths,

- hardware to support Cipher Block Chaining (CBC), Cipher Feedback (CFB),

Output Feedback (OFB) and Counter (CTR) modes of operation for symmetric-key cryptographic block ciphers,

- hardware to support Galois/Counter Mode (GCM) of operation and Galois Message Authentication Code (GMAC) for symmetric-key cryptographic block ciphers,

- hardware to calculate Cyclic Redundancy Checks (CRC),

- · hardware to serve with True Random Numbers,

- hardware and service software to control access to memories and hardware components.

In addition, SN100\_SE embeds sensors, which ensure proper operating conditions of the device. Integrity protection of data and code involves error correction and error detection codes, light sensing and other security functionality. Encryption and masking

mechanisms are implemented to preserve confidentiality of data and code. The IC hardware is shielded against physical attacks.

Note that the SN100\_SE also implements PUF functionality. However this hardware functionality is not in the scope of evaluation.

## 1.3.1.2 Security Software

The IC Dedicated Software provides Security Software that can be used by the Security IC Embedded Software. The Security Software is composed of Services Software and Crypto Library.

The **Services Software** consists of Flash Services Software, Services Framework Software and the part of the Services HAL (Hardware Abstraction Layer) that is not stored to ROM. The Flash Services Software manages technical demands of the Flash memory and serves the Security IC Embedded Software with an interface for Flash erase and/or programming. The Services Framework Software represents a collection of different abstractions and utility functions that provide a runtime environment to the individual Services. The Services HAL provides an interface for the Services Software to the hardware that controls the Flash memory.

The Services Software is considered part of the Service Code and is stored in the Flash memory of the TOE.

The **Crypto Library** consists of several binary packages that are pre-loaded to the Flash memory of the TOE for usage by the Security IC Embedded Software. The Crypto Library provides

- AES

- Triple-DES (3DES)

- RSA

- · RSA key generation

- · RSA public key computation

- ECDSA (ECC over GF(p)) signature generation and verification

- ECC over GF(p) key generation

- ECDH (ECC Diffie-Hellmann) key exchange

- MontDH (Diffie Hellman key exchange on Montgomery Curves over GF(p)) key generation

- MontDH (Diffie Hellman key exchange on Montgomery Curves over GF(p)) key exchange

- EdDSA (Edwards-curve Digital Signature Algorithm) signature generation and verification

- EdDSA (Edwards-curve Digital Signature Algorithm) key generation

- · ECDAA related functions

- Full point addition (ECC over GF(p))

- Standard security level SHA-1, SHA-224, SHA-256, SHA-384, SHA-512, SHA-3/224, SHA-3/256, SHA-3/384, SHA-3/512 algorithms

- High security level SHA-1, SHA-224, SHA-256, SHA-384, SHA-512, SHA-3/224, SHA-3/256, SHA-3/384, SHA-3/512 algorithms

- HMAC algorithms

- eUICC authentication functions (MILENAGE, TUAK and CAVE)

In addition, the Crypto Library implements a software (pseudo) random number generator which is initialized (seeded) by the hardware random number generator of the TOE. The Crypto Library also provides a secure copy routine, a secure memory compare routine, cyclic redundancy check (CRC) routines, and includes internal security measures for residual information protection.

Note that the Crypto Library v1.0.0 also implements

- KoreanSeed

- OSCCA SM2, OSCCA SM3 and OSCCA SM4

- Felica

However these library elements are not in the scope of evaluation.

The Crypto Library is considered part of the Shared Library functions and is stored in the Flash memory of the TOE.

## **1.3.2 TOE Type**

The TOE is a Security Integrated Circuit Platform for various operating systems and applications with high security requirements.

## 1.3.3 Security During Development and Production

The Security IC product life cycle is scheduled in phases, which are defined in the Protection Profile [5].

Phase 2 *IC Development*, phase 3 *IC Manufacturing* as well as phase 4 *IC Packaging* of this life cycle are part of this Security Target. The TOE Delivery is at the end of phase 4.

The development environment of SN100\_SE always ranges from phase 2 *IC Development* to TOE Delivery. All other phases are part of the operational environment. This addresses Application Note 1 in the Protection Profile [5].

In phase 2 *IC Development* of SN100\_SE access to sensitive design data of SN100\_SE is restricted to people, who are involved in the development of the product.

In phase 3 *IC Manufacturing* the TOE as integral part of SN100x IC are produced and tested on wafers. In this phase NXP also serves as Composite Product Manufacturer by optionally storing Security IC Embedded Software to the Flash of SN100\_SE. The NXP Trust Provisioning Service ensures confidentiality and integrity of any customer data in this phase. This incudes secure treatment and insertion of data and code received from the customer as well as random or derived data, which are generated by NXP.

In phase 4 IC Packaging SN100x ICs including the TOE are embedded into packages.

The delivery processes between all involved sites provide accountability and traceability of the dies. Authentic delivery of the TOE is supported by its NXP Trust Provisioning Service as described in [39].

## 1.3.4 Required non-TOE Hardware/Software/Firmware

Besides the SN100\_SE the SN100x Single Chip Secure Element and NFC Controller comprises a NFC controller (SN100\_NFC) and a shared Power Management Unit (SN100\_PMU).

For operation the SN100\_SE requires full function of the SN100\_PMU subsystem, that is controlled by software of the SN100\_NFC subsystem (see <u>Figure 1</u>).

SN100 Series - Secure Element with Crypto Library

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

The TOE does not include communication drivers in the IC Dedicated Support Software. Those need to be part of the Security IC Embedded Software.

## 1.4 TOE Description

## 1.4.1 Physical Scope of TOE

The SN100x IC is build upon two subsystems: "SN100 SE" and "SN100 NFC". Both subsystem use a shared Power Management Unit ("SN100 PMU"). The toplevel block diagram of SN100x is depicted in Figure 1.

The SN100 SE subsystem is built of IC hardware and IC Dedicated Software, and includes documentation. A block diagram of the TOE and its interfaces is depicted in Figure 2.

The IC Dedicated Software of SN100 SE comprises

- · IC Dedicated Support Software, composed of

- Test software named Factory OS

- Boot software named Boot OS

- Memory Driver software named Flash Driver Software

- · Security Software, composed

- Services Software named Services Software

- Library Software named Crypto Library

All other software is called Security IC Embedded Software and is not part of the TOE.

## 1.4.2 Evaluated Configurations

Each configuration of the TOE consists of a physical configuration (i.e. hardware component incl. ROM code and related documentation) and a logical configuration (i.e. Software components and configuration data stored to Flash memory).

The definition of the configuration identifiers of SN100 SE is detailed in Table 1.

Table 1. Configuration identifiers of the TOE

| Name                                   | Symbol | Description                                                                                                                                                                                                                                                     |

|----------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Series                                 | srs    | Series identifier in NXP product family                                                                                                                                                                                                                         |

| y: fixed metal ma<br>z: customizable r |        | <ul> <li>x: base layer identifier of the development type</li> <li>y: fixed metal masks identifier of the development type</li> <li>z: customizable metal masks identifier of the development type, includes the IC Dedicated Software stored to ROM</li> </ul> |

| NXP software                           | wn     | w: NXP software combination identifier of the development type, identifies the IC Dedicated Software stored to Flash n: version identifier of the NXP software combination, identifies software version data stored to Flash                                    |

| NXP hardware configuration             | V      | Version identifier of the NXP hardware configuration, identifies the version of configuration data stored to Flash                                                                                                                                              |

The symbols in the second column in <u>Table 1</u> build the product name of a physical configuration according to the following rule:

srs xy.z wnv

Evaluated physical configuration of the TOE is

• SN100\_SE **B2.1**

This subsystem in integral part of any variant of the SN100x Single Chip Secure Element and NFC Controller Series IC version B2.1. <sup>3</sup>

All components of SN100\_SE B2.1 that are common for all logical configurations are listed in <u>Table 2</u> with their respective version numbers.

Evaluated logical configurations of the TOE stored to flash memory are

- SN100\_SE **B2.1 C25**

- SN100\_SE **B2.1 C48**

- SN100\_SE **B2.1 C58**

All components that are specific for a certain configuration are given in <u>Table 3</u> (for SN100\_SE B2.1 C25), <u>Table 4</u> (for SN100\_SE B2.1 C48) and <u>Table 5</u> (for SN100\_SE B2.1 C58).

Table 2. Components common for all SN100\_SE B2.1

| Category             | Component                        | Identification | Delivery form                                  |

|----------------------|----------------------------------|----------------|------------------------------------------------|

| IC Hardware          | base layer and fixed metal masks | B2.1           | Package                                        |

| IC Dedicated Support | Factory OS                       | 4.2.0          | On-chip software. Stored to the ROM of the TOE |

| Software             | Boot OS                          | 4.2.0          | On-chip software. Stored to the ROM of the TOE |

3 The "x" in SN100x indicates the type of the SN100 series (representing the NFC Controller configuration)

SN100 Series - Secure Element with Crypto Library

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

| Category Component I                       |                                                                          | Identification | Delivery form                                  |

|--------------------------------------------|--------------------------------------------------------------------------|----------------|------------------------------------------------|

| Flash Driver Software                      |                                                                          | 4.0.8          | On-chip software. Stored to the ROM of the TOE |

| Documentation, Product Data Sheet          | SN100x_SE High-performance secure element subsystem, Product data sheet  | [14]           | Electronic Document (PDF via NXP Docstore)     |

|                                            | SN100x_SE - SFR Tables for Berlin core                                   | [41]           | Electronic Document (PDF via NXP Docstore)     |

| Documentation, Product Data Sheet Addendum | SN100x Wafer and Delivery Specification, Product data sheet addendum     | [15]           | Electronic Document (PDF via NXP Docstore)     |

|                                            | P73 family SC300 User Manual, Product Data sheet addendum                | [16]           | Electronic Document (PDF via NXP Docstore)     |

|                                            | P73 family DMA Controller PL080 User manual, Product data sheet addendum | [17]           | Electronic Document (PDF via NXP Docstore)     |

|                                            | P73 Family Chip Health Mode, Application note                            | [18]           | Electronic Document (PDF via NXP Docstore)     |

|                                            | P73 Family Code Signature Watchdog, Application note                     | [19]           | Electronic Document (PDF via NXP Docstore)     |

|                                            | ARM®v7-M Architecture Reference<br>Manual                                | [40]           | Electronic Document (www.arm.com)              |

Table 3. Components of SN100 SE B2.1 specific for C25

| Category                                      | Component                                                         | Identification | Delivery form                                                   |

|-----------------------------------------------|-------------------------------------------------------------------|----------------|-----------------------------------------------------------------|

| Configuration Data                            | Factory Page                                                      | 18218          | On-chip configuration page. Stored to the FLASH area of the TOE |

|                                               | System Page Common                                                | 18468          | On-chip configuration page. Stored to the FLASH area of the TOE |

|                                               | BootOS Patch                                                      | 4.2.0 PL3 v4   | On-chip configuration page. Stored to the FLASH area of the TOE |

| Security Software                             | Services Software                                                 | 4.13.3.0       | On-chip software. Stored to the FLASH area of the TOE           |

|                                               | Crypto Library                                                    | 1.0.0          | On-chip software. Stored to the FLASH area of the TOE           |

| Documentation, User<br>Guidance and Operation | SN100_SE Information on Guidance and Operation                    | [10]           | Electronic Document (PDF via NXP Docstore)                      |

| Manual                                        | SN100 Services User Manual - API and Operational Guidance         | [11]           | Electronic Document (PDF via NXP Docstore)                      |

|                                               | SN100 Services Addendum - Additional API and Operational Guidance | [12]           | Electronic Document (PDF via NXP Docstore)                      |

|                                               | SN100x Crypto Library Information on Guidance and Operation       | [13]           | Electronic Document (PDF via NXP Docstore)                      |

| Documentation, User                           | User Manual: RNG                                                  | [20]           | Electronic Document (PDF via NXP Docstore)                      |

| Manuals Crypto Library                        | User Manual: Utils                                                | [34]           | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: SymCfg                                               | [33]           | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: RSA                                                  | [27]           | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: RSA Key Generation                                   | [28]           | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: ECC over GF(p)                                       | [29]           | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: ECDAA                                                | [30]           | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: SHA                                                  | [22]           | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: SecSHA                                               | [23]           | Electronic Document (PDF via NXP Docstore)                      |

| Category | Component                 | Identification | Delivery form                              |

|----------|---------------------------|----------------|--------------------------------------------|

|          | User Manual: SHA3         | [24]           | Electronic Document (PDF via NXP Docstore) |

|          | User Manual: SecSHA3      | [25]           | Electronic Document (PDF via NXP Docstore) |

|          | User Manual: HMAC         | [26]           | Electronic Document (PDF via NXP Docstore) |

|          | User Manual: HASH         | [21]           | Electronic Document (PDF via NXP Docstore) |

|          | User Manual: TwdEdMontGfp | [31]           | Electronic Document (PDF via NXP Docstore) |

|          | User Manual: eUICC        | [32]           | Electronic Document (PDF via NXP Docstore) |

|          | Errata Sheet              | [37]           | Electronic Document (PDF via NXP Docstore) |

Table 4. Components of SN100\_SE B2.1 specific for C48

| Category                                      | Component Identi                                                  |               | Delivery form                                                   |

|-----------------------------------------------|-------------------------------------------------------------------|---------------|-----------------------------------------------------------------|

| Configuration Data                            | Factory Page                                                      | 18652         | On-chip configuration page. Stored to the FLASH area of the TOE |

|                                               | System Page Common                                                | 18468         | On-chip configuration page. Stored to the FLASH area of the TOE |

|                                               | BootOS Patch                                                      | 4.2.0 PL5 v16 | On-chip configuration page. Stored to the FLASH area of the TOE |

| Security Software                             | Services Software                                                 | 4.13.7.1      | On-chip software. Stored to the FLASH area of the TOE           |

|                                               | Crypto Library                                                    | 1.0.0         | On-chip software. Stored to the FLASH area of the TOE           |

| Documentation, User<br>Guidance and Operation | SN100_SE Information on Guidance and Operation                    | [10]          | Electronic Document (PDF via NXP Docstore)                      |

| Manual                                        | SN100 Services User Manual - API and Operational Guidance         | [11]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | SN100 Services Addendum - Additional API and Operational Guidance | [12]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | SN100x Crypto Library Information on Guidance and Operation       | [13]          | Electronic Document (PDF via NXP Docstore)                      |

| Documentation, User                           | User Manual: RNG                                                  | [20]          | Electronic Document (PDF via NXP Docstore)                      |

| Manuals Crypto Library                        | User Manual: Utils                                                | [34]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: SymCfg                                               | [33]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: RSA                                                  | [27]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: RSA Key Generation                                   | [28]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: ECC over GF(p)                                       | [29]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: ECDAA                                                | [30]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: SHA                                                  | [22]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: SecSHA                                               | [23]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: SHA3                                                 | [24]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: SecSHA3                                              | [25]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: HMAC                                                 | [26]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: HASH                                                 | [21]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: TwdEdMontGfp                                         | [31]          | Electronic Document (PDF via NXP Docstore)                      |

|                                               | User Manual: eUICC                                                | [32]          | Electronic Document (PDF via NXP Docstore)                      |

| Category | Component    | Identification | Delivery form                              |

|----------|--------------|----------------|--------------------------------------------|

|          | Errata Sheet | [37]           | Electronic Document (PDF via NXP Docstore) |

Table 5. Components of SN100 SE B2.1 specific for C58

| tory Page tem Page Common tOS Patch vices Software oto Library | 18652<br>18468<br>4.2.0 PL5 v16<br>4.14.0.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | On-chip configuration page. Stored to the FLASH area of the TOE  On-chip configuration page. Stored to the FLASH area of the TOE  On-chip configuration page. Stored to the FLASH area of the TOE  On-chip software. Stored to the FLASH area of                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tOS Patch<br>vices Software                                    | 4.2.0 PL5 v16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | area of the TOE  On-chip configuration page. Stored to the FLASH area of the TOE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| vices Software                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | area of the TOE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                | 4.14.0.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | On chin coftware Stored to the ELASH area of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| oto Library                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | the TOE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                | 2.0.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | On-chip software. Stored to the FLASH area of the TOE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 00_SE Information on Guidance and ration                       | [10]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 00 Services User Manual - API and rational Guidance            | [11]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 00 Services Addendum - Additional and Operational Guidance     | [12]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 00x Crypto Library Information on dance and Operation          | [13]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: RNG                                                  | [20]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: Utils                                                | [34]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: SymCfg                                               | [33]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: RSA                                                  | [27]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: RSA Key Generation                                   | [28]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: ECC over GF(p)                                       | [29]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: ECDAA                                                | [30]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: SHA                                                  | [22]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: SecSHA                                               | [23]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: SHA3                                                 | [24]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: SecSHA3                                              | [25]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: HMAC                                                 | [26]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: HASH                                                 | [21]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: TwdEdMontGfp                                         | [31]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: eUICC                                                | [32]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: UtilsMath                                            | [35]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Manual: KDF                                                  | [36]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ta Sheet                                                       | [37]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Electronic Document (PDF via NXP Docstore)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r (                                                            | action  20 Services User Manual - API and rational Guidance  20 Services Addendum - Additional and Operational Guidance  20 Services Addendum - Additional and Operational Guidance  20 Services Addendum - Additional and Operational Guidance  20 Services Addendum - Additional and Operation on ance and Operation  Manual: RNG  Manual: RNG  Manual: SymCfg  Manual: SymCfg  Manual: RSA Key Generation  Manual: ECC over GF(p)  Manual: ECDAA  Manual: SHA  Manual: SecSHA  Manual: SecSHA  Manual: HMAC  Manual: HMAC  Manual: TwdEdMontGfp  Manual: GUICC  Manual: UtilsMath  Manual: KDF | action  O Services User Manual - API and rational Guidance  O Services Addendum - Additional and Operational Guidance  O Services Addendum - Additional and Operational Guidance  O Crypto Library Information on ance and Operation  Manual: RNG  Manual: Utils  Manual: SymCfg  Manual: RSA  Manual: RSA  Manual: RSA Key Generation  Manual: ECC over GF(p)  Manual: ECDAA  Manual: SHA  Manual: SecSHA  Manual: SecSHA  Manual: SecSHA  Manual: SecSHA  Manual: HMAC  Manual: HMAC  Manual: TwdEdMontGfp  Manual: OtilsMath  Manual: UtilsMath  Manual: KDF  Manual: KDF |

Logical configuration options are provided for each physical configuration of SN100\_SE, which do not modify the physical scope described in <u>Section 1.4.1</u>. Evaluated logical

configuration options are all or a subset of the order entry options available in the electronic Order Entry Form [38].

<u>Table 6</u> identifies these evaluated logical configuration options. These options are detailed in [14].

Table 6. Evaluated logical configuration options

| Name of order entry option     | Evaluated values |

|--------------------------------|------------------|

| SNSE_HWOPT_ENABLE_ISORESET     | YES/NO           |

| SNSE_SWOPT_ENABLE_CHMODE       | YES/NO           |

| SNSE_SWOPT_REENABLE_TESTMODE   | YES/NO           |

| SNSE_SWOPT_ENABLE_APPDISABLE   | YES/NO           |

| SNSE_SWOPT_SELECT_MODE         | AAP              |

| SNSE_HWOPT_SELECT_RAM_HS_START | [00xFF]          |

| SNSE_HWOPT_SELECT_RAM_HS_END   | [00xFF]          |

The logical configuration options given in <u>Table 6</u> are complemented with additional evaluated logical configuration options. These are not selectable by the customer via electronic Order Entry Form, but are exclusively under control of NXP.

The TOE as integral part of SN100x IC is delivered as a packaged device. The security of the TOE does not rely on the way the pads are connected to the package. Therefore the security functionality of SN100\_SE is not affected by the delivered package type.

The only available package type is "Wafer Level Chip Scale Package" (WLCSP). This package is a thin fine-pitch ball grid array package.

The commercial type name of the SN100x IC reflects package type in the name. It is assigned according to the following format:

SN100 b pp(p) / x y zz ff

The commercial type name of a physical configuration is built by replacing the symbols in the above format with the values identified in Table 7.

Table 7. Values of symbols in commercial type name

| Symbol | Value                                             | Description                                                                                                                                                                                      |  |

|--------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| srs    | SN100                                             | Series in NXP product family                                                                                                                                                                     |  |

| b      | X                                                 | Basic type in the series of NXP product family, defining e.g. the NFC host interface                                                                                                             |  |

| pp(p)  | UK                                                | Package type UK = Wafer Level Chip Scale Package (WLCSP)                                                                                                                                         |  |

| X      | В                                                 | Base layer identifier                                                                                                                                                                            |  |

| У      | 2                                                 | Fixed metal masks identifier                                                                                                                                                                     |  |

| zz     | 1                                                 | ROM Mask reference                                                                                                                                                                               |  |

| ff     | Two characters (each either a letter or a number) | FabKey Number (FKN), which identifies the contents in AP-Flash at TOE Delivery, and the selection of logical configuration options, processed by Order Entry Form Tool individually for each OEF |  |

Information on how to order SN100x and how to identify the logical configuration options of the SN100 SE after TOE Delivery is described in [14].

The TOE is integral part of the SN100x IC. Note that SN100x without any Security IC Embedded Software for the TOE is available for NXP internal use only.

The manufacturing process of SN100x allows options that can be selected by NXP in the electronic Order Entry Form [38]. The evaluated options are given in Table 8

Table 8. Evaluated options of manufacturing process (NXP internal only)

| Name of order entry option | Evaluated values                |

|----------------------------|---------------------------------|

| Diffusion Fab              | GF7 / GF1 / SMIC <sup>[1]</sup> |

<sup>[1]</sup> Wafers from sites GF1 and SMIC will be used for logical configurations C48/C58 only

The delivery method used for SN100x and information on how to identify the selected manufacturing options are described in [15].

## 1.4.3 Logical Scope of TOE

#### 1.4.3.1 Hardware Description

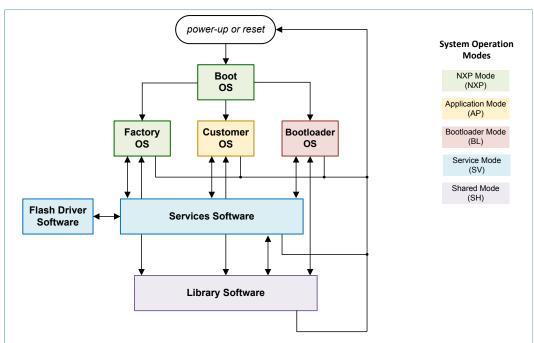

The hardware of SN100\_SE facilitates seven types of software components, which are depicted in Figure 3.

Figure 3. Types of software components and system operation modes facilitated by the hardware

The hardware always starts-up with executing the Boot OS. The Boot OS finally jumps to a start address in either Factory OS, Customer OS or Bootloader OS. The hardware provides no other way to start these operating systems but via power-up or reset of the device. Not more than one operating system out of Factory OS, Customer OS and Bootloader OS can be executed per start-up cycle. Each of the operating systems may

interact with and with Library Software according to the programming interface they respectively provide.

The Factory OS implements security functionality against unauthorized access in the field. Startup into Bootloader OS is blocked by the TOE with order entry option = AAP until Customer OS explicitly unblocks this with next startup by changing the logical configuration to = BOR. Then Bootloader OS can reactivate this blockage with changing back to = AAP. Instead, order entry option = BOR causes the TOE to start-up into Bootloader OS when a special sequence is applied to a pad.

Jumps between types of software components imply transformations in system operation modes, which are under control of the hardware. The hardware distinguishes among five such system operation modes. These are named NXP Mode (NXP), Application Mode (AP), Bootloader Mode (BL), Service Mode (SV) and Shared Mode (SH). Figure 3 gives the basic assignment of system operation modes to the seven types of software components.

Transformations among NXP Mode, Bootloader Mode, Application Mode and Service Mode are usually transitions from one to another system operation mode. Exceptions are with logical configurations EN\_SV\_AP=YES, EN\_SV\_BL=YES and/or EN\_BL\_FOR\_AP=YES. Logical configuration EN\_SV\_AP=YES resp. EN\_SV\_BL=YES enable Bootloader OS to also activate Application Mode resp. Bootloader Mode when it jumps to Services Software. These configurations fit to the needs of update functionality in a Bootloader OS provided by NXP for secure updates of Security IC Embedded Software. *Such Bootloader OS itself is not in scope of this TOE*. In logical configuration EN\_BL\_FOR\_AP=YES the TOE always sets both, Application Mode and Bootloader Mode when jumping to Customer OS. This configuration is appropriate for NXP operating systems with integrated update functionality in the field. Such NXP operating systems themselves are not in scope of this TOE.

Shared Mode is always activated in addition to the system operation mode(s) of the software component type that jumps to Library Software. This allows to share Library Software among different types of software components.

System operation modes are used by the hardware to control access to memories and hardware components. The software component types are stored to different areas in the Flash memory, which are assigned with access rights that fit to their related software component type.

Furthermore, the ARM SC300 processor supports two CPU modes named "thread" and "handler", and also two CPU privilege levels named privileged and unprivileged (of which the latter one is also called "user" by ARM). These choices are combined to three valid CPU operation modes, which are privileged thread, unprivileged thread and privileged handler. The SC300 processor implements these CPU operation modes to control access to some of its configuration registers and instructions. Use of the two modes thread and handler is limited to the SC300 processor whereas the privilege levels are also used in the system to control access to memories and hardware components.

SN100\_SE implements 64 Kbytes ROM, 2 Mbytes Flash, 52 Kbytes System RAM, 5 Kbytes PKC RAM and a Buffer RAM for Flash erase/programming and for Flash read caching. All these memories are accessible over the bus system on data/address busses, and the PKC RAM can also be directly accessed by the PKC coprocessor on a separate data/address bus. PKC RAM accesses are arbitrated in the RAM Controller. The hardware controls access to the memories over the bus system. Direct access to the PKC RAM is controlled by way of access control to the hardware component PKC coprocessor. Access to the PKC RAM by the CPU and the PKC coprocessor over the bus system is adjusted accordingly.

The hardware controls write, read and execute access to the memories over the bus system against system operation modes. This is done based on segments in the logical address space. In this context the whole ROM address space is reserved for NXP.